本篇講解如何在vscode中進行verilog編譯及測試流程

以下安裝流程在 windows11沙盒 中進行

基本 simulation 功能

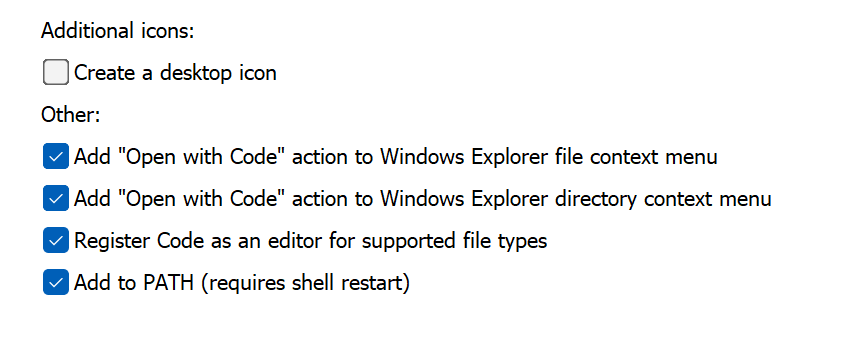

- 下載並安裝vscode

另外建議勾選context menu 以及 add path

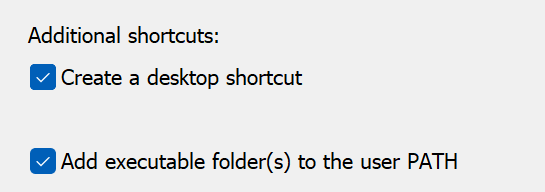

- 下載 並安裝 Icarus Verilog

這邊我選用 iverilog-v11-20210204-x64_setup.exe [44.1MB]

使用 Full installation, 並勾選 add to path

安裝完記得重開VScode - vscode安裝 mshr-h 的 Verilog-HDL/SystemVerilog/Bluespec SystemVerilog

- vscode安裝 WaveTrace

- vscode安裝 Code Runner

- vscode -> File -> Preferences -> Settings -> 右上角 Open Setting (JSON)

// For verilog using

"code-runner.saveFileBeforeRun": true,

"code-runner.executorMapByGlob": {

"*.v": "cd $dir && iverilog -o run.vvp \"$fileName\" && vvp run.vvp",

"*.vcd": "cd $dir && gtkwave \"$fileName\"",

}, - vscode 開啟任意 testbench 檔案

module test (

input clk,

input a,

input b,

output reg c

);

always @(posedge clk) begin

c = a ^ b;

end

endmodule

module tb_test;

// test Parameters

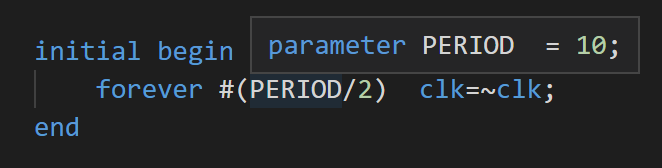

parameter PERIOD = 10;

// test Inputs

reg clk = 0 ;

reg a = 0 ;

reg b = 0 ;

// test Outputs

wire c ;

initial begin

forever #(PERIOD/2) clk=~clk;

end

test u_test (

.clk ( clk ),

.a ( a ),

.b ( b ),

.c ( c )

);

initial

begin

$dumpfile("test_tb.vcd");

$dumpvars();

#10 a = 0; b =0;

#10 a = 0; b =1;

#10 a = 1; b =0;

#10 a = 1; b =1;

#10 $finish;

end

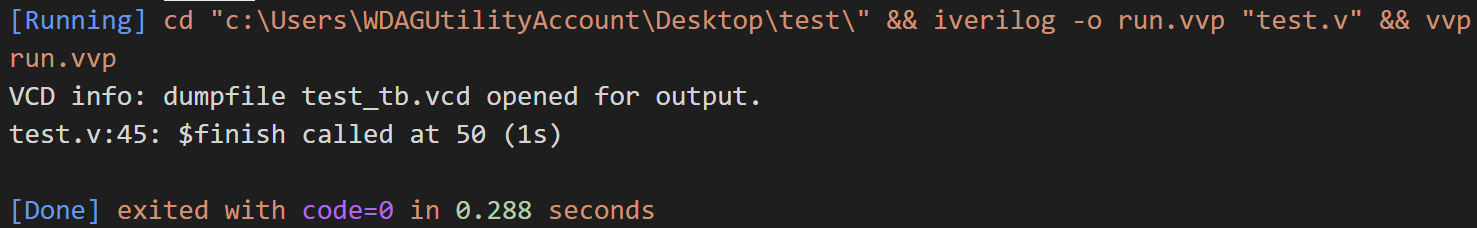

endmodule - 按下

Ctrl + Alt + N應該會出現如下輸出:

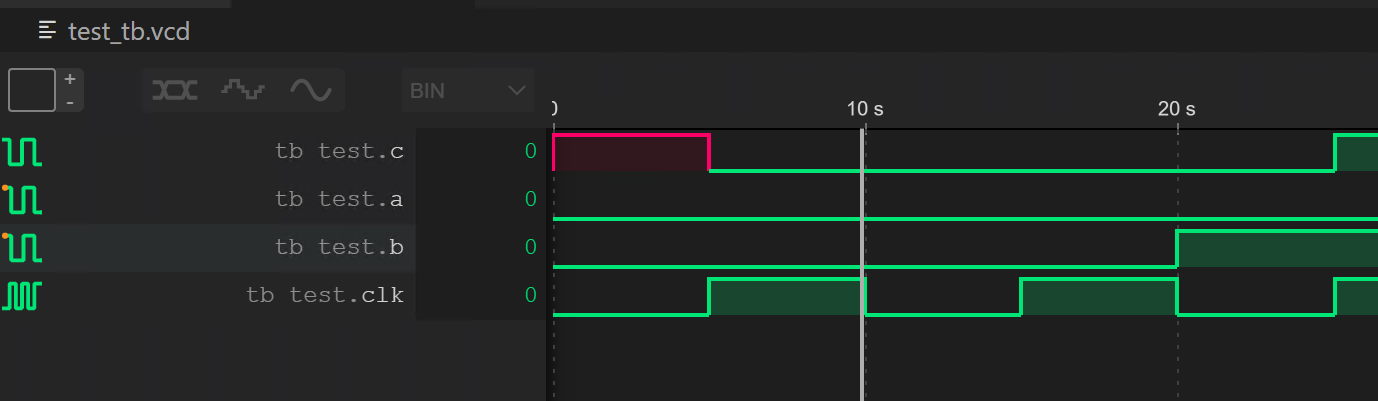

- 打開.vcd檔案,按

Add signals並添加欲觀察之訊號, 會看到如下圖結果。如果有 iverilog錯誤 請確認是否第2步有勾選path選項.

額外 Ctags Integration 功能

- 如果需要intellsense之類的功能, 請安裝 ctags於

assets中下載x64的版本 - 將

ctags-2021-10-25_p5.9.20211024.0-2-g6f544dfc-x64.zip內容解壓縮放到任意目錄, 例如c:\ctags, 確保該目錄下有ctags執行檔 - 在系統環境變數中添加目錄, 在這個範例中就是

c:\ctags - 重新啟動vscode, 應該就會看到如下圖所示之效果